susctf(DigitalCircuits+hello_word)

SUSCTF(DigitalCircuits+hello_word)

DigitalCircuits

这是一个pyc反编译的题目

pyc文件转换成py文件

这是一个将pyc打包成地exe文件,首先使用软件解包,这个软件反编译出来地主程序并不是一个pyc文件,需要自己通过instruct这个文件修改这个文件地格式

将pyc文件用unemployed6 编译为py文件,然后得到源代码,分析代码,发现这是一个tea加密

1 | # uncompyle6 version 3.8.1.dev0 |

tea算法

tea 的密钥是:0x4445,0x4144,0x4245,0x4546

最后的加密结果:[0x3e8947cb,0xcc944639,0x31358388,0x3b0b6893,0xda627361,0x3b2e6427]

dalt:0x9e3779b9

脚本:

1 | #include <bits/stdc++.h> |

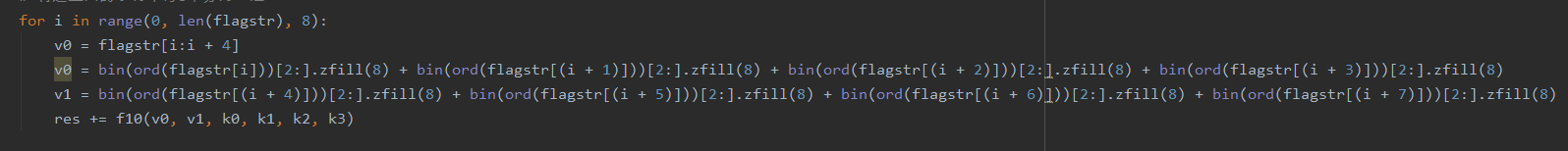

在输入数据的时候:从图中我们可以看到每组字符串中(每4个字符为一组)它将低位的字符放到二进制的高位,所以最后的结果还需要调整字符串的顺序,逆序取出每组数据

最后的flag是 SUSCTF{XBvfaEdQvbcrxPBh8AOcJ6gA}

hello_word

这个题目考察vhdl

定位代码

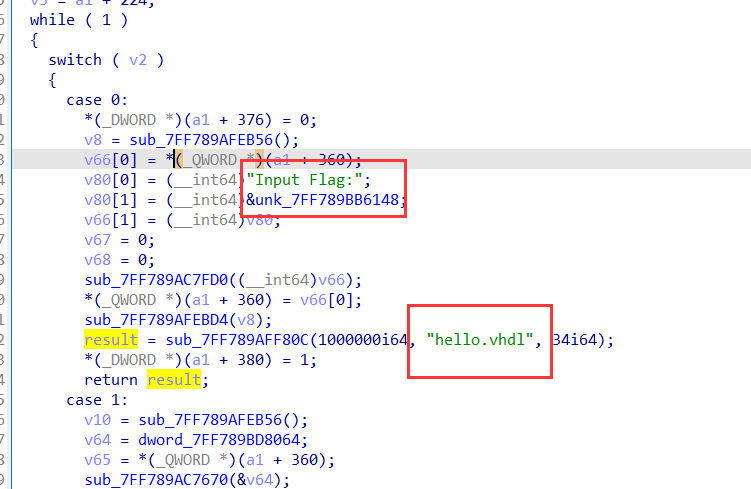

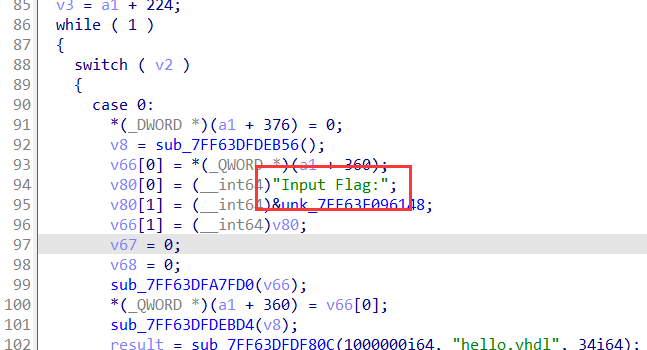

通过字符串找到一个含有inputflag页面的函数,在里面出现了有vhdl

VHDL介绍

GHDL是一个基于GCC的VHDL语言编译/模拟命令行工具

通过使用代码生成器(LLVM、GCC或仅x86_64 / i386,内置的),它比任何解释模拟器都要快得多。它可以处理非常大的设计,例如leon3/grlib。

可将波形写入GHW、VCD或 FST 文件。结合基于GUI的波形查看器和良好的文本编辑器,GHDL 是用于编写、测试和模拟代码的非常强大的工具。

状态机介绍

分析代码这是一个状态机

有限状态机(Finite-state machine,FSM):又称有限状态自动机,简称状态机,是表示有限个状态以及在这些状态之间的转移和动作等行为的数学模型。

FSM:是一种算法思想,简单而言,有限状态机由一组状态、一个初始状态、输入和根据输入及现有状态转换为下一个状态的转换函数组成。

六种元素:起始、终止、现态、次态(目标状态)、动作、条件,我们就可以完成一个状态机图

状态机,也就是 State Machine ,不是指一台实际机器,而是指一个数学模型。说白了,一般就是指一张状态转换图。

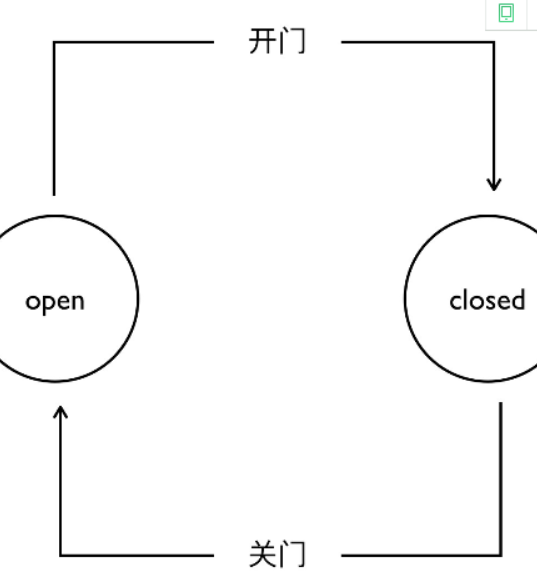

例如:自动门有两个状态,open 和 closed ,closed 状态下,如果读取开门信号,那么状态就会切换为 open 。open 状态下如果读取关门信号,状态就会切换为 closed 。

能够抽象出来的图:

状态机的四大概念:

- 第一个是 State ,状态。一个状态机至少要包含两个状态。例如上面自动门的例子,有 open 和 closed 两个状态。

- 第二个是 Event ,事件。事件就是执行某个操作的触发条件或者口令。对于自动门,“按下开门按钮”就是一个事件。

- 第三个是 Action ,动作。事件发生以后要执行动作。例如事件是“按开门按钮”,动作是“开门”。编程的时候,一个 Action一般就对应一个函数。

- 第四个是 Transition ,变换。也就是从一个状态变化为另一个状态。例如“开门过程”就是一个变换。

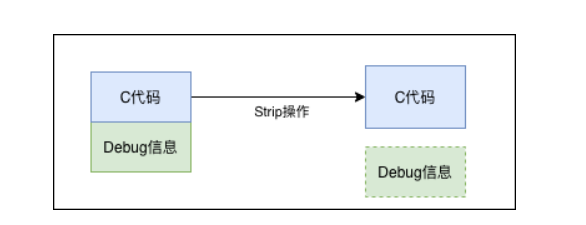

strip

这道题是被strip了的,下面是对strip概念的解释

strip的作用:

so文件组成:一个完整的 so 由C代码加一些 debug 信息组成,这些debug信息会记录 so 中所有方法的对照表,就是方法名和其偏移地址的对应表,也叫做符号表。

未strip的so文件:这种既有c代码和debug信息的 so文件就是未 strip 的so文件,通常体积会比较大

strip操作:so 中的debug信息会被剥离,整个 so 的体积也会缩小。

strip操作解说:

逻辑电路

逻辑电路一般是状态机

逻辑电路:是指完成逻辑运算的电路。这种电路,一般有若干个输入端和一个 或几个输出端,当输入信号之间满足某一特定逻辑关系时,电路就开通,有输 出;否则,电路就关闭,无输出。所以,这种电路又叫逻辑门电路,简称门电路。

这里的case语句展示了这样的逻辑电路的构成

这里考察的是VHDL这个程序

case语句的代码的算法分析

定位代码

首先通过字符串inputflag定位到对应的函数,这是一个switch的循环语句

分析这个switch语句

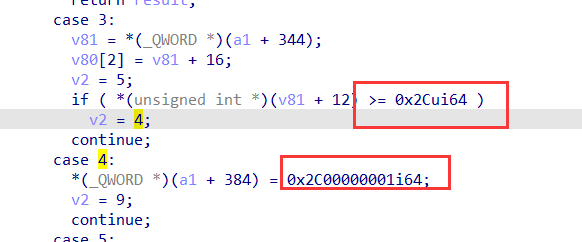

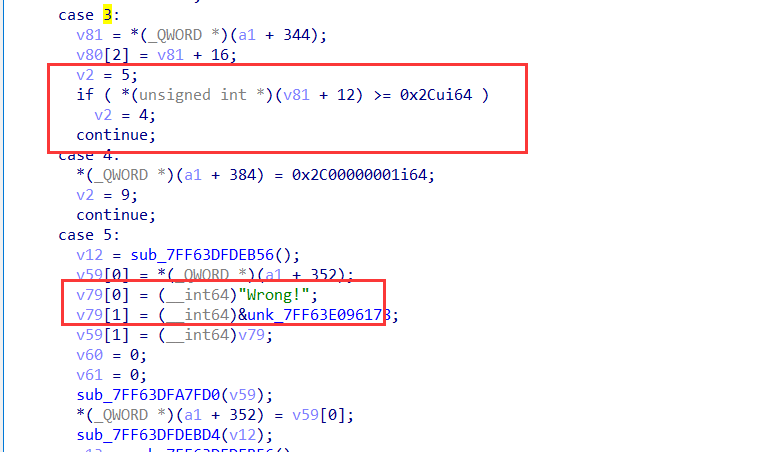

case1-4

case1-4不断地跳转,这个地方地代码是对输入地flag的长度赋值

向下跳转到case9的地方

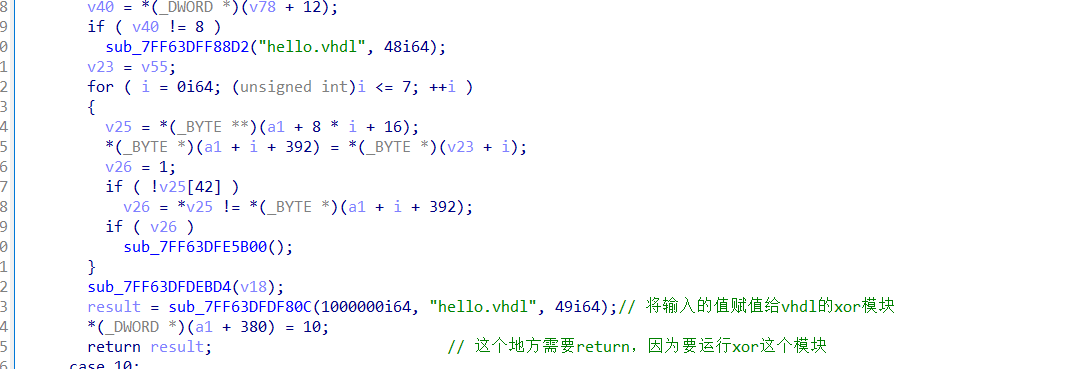

case9模块

这个地方把输入的值给到vhdl中进行xor模块,然后跳到case10模块

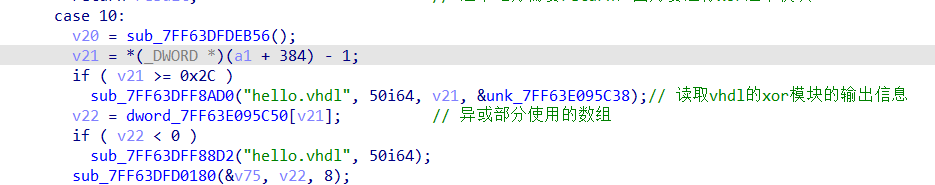

case10模块

调用vhdl的异或的方法,并且在这里可以知道一个用于异或运算的数组

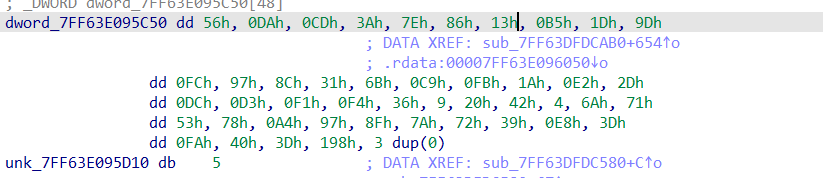

数组是

1 | [0x56,0xda,0xcd,0x3a,0x7e,0x86,0x13,0xb5,0x1d,0x9d,0xfc,0x97,0x8c,0x31,0x6b,0xc9,0xfb,0x1a,0xe2,0x2d,0xdc,0xd3,0xf1,0xf4,0x36,0x09,0x20,0x42,0x04,0x6a,0x71,0x53,0x78,0xa4,0x97,0x8f,0x7a,0x72,0x39,0xe8,0x3d,0xfa,0x40,0x3d,0x98,0x01] |

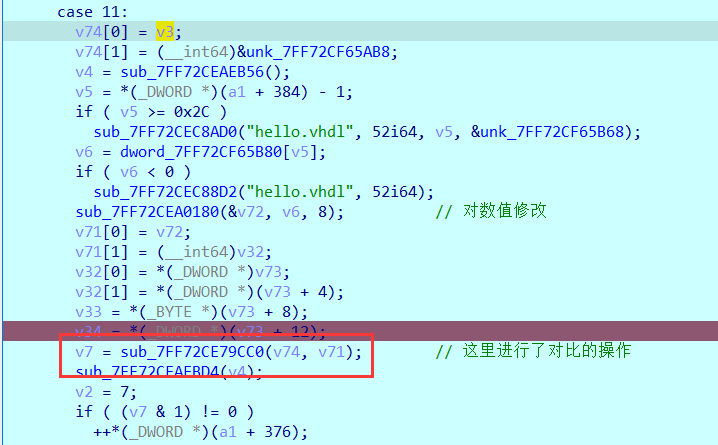

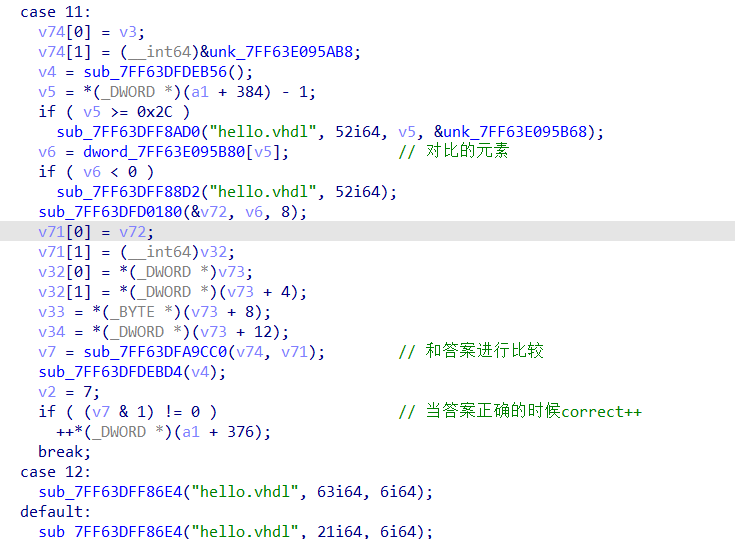

case11

将异或的结果和最后的答案对比

对比使用的数组:

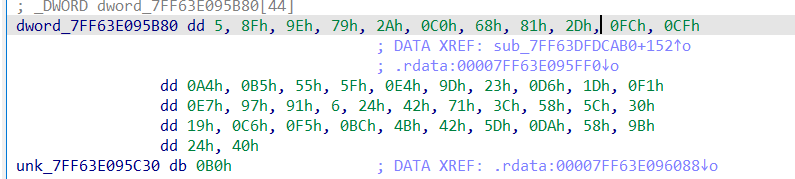

数组:

1 | [0x05,0x8f,0x9e,0x79,0x2a,0xc0,0x68,0x81,0x2d,0xfc,0xcf,0xa4,0xb5,0x55,0x5f,0xe4,0x9d,0x23,0xd6,0x1d,0xf1,0xe7,0x97,0x91,0x06,0x24,0x42,0x71,0x3c,0x58,0x5c,0x30,0x19,0xc6,0xf5,0xbc,0x4b,0x42,0x5d,0xda,0x58,0x9b,0x24,0x40] |

case 5模块

通过表示正确字符个数的correct判断最后的结果,错误就跳转到wrong的case5这个模块

脚本:

1 | obj1 = [0x05,0x8f,0x9e,0x79,0x2a,0xc0,0x68,0x81,0x2d,0xfc,0xcf,0xa4,0xb5,0x55,0x5f,0xe4,0x9d,0x23,0xd6,0x1d,0xf1,0xe7,0x97,0x91,0x06,0x24,0x42,0x71,0x3c,0x58,0x5c,0x30,0x19,0xc6,0xf5,0xbc,0x4b,0x42,0x5d,0xda,0x58,0x9b,0x24,0x40] |

所以最后的flag是 SUSCTF{40a339d4-f940-4fe0-b382-cabb310d2ead}